Hay guise.

This is my senior project, figured I'd share it. I'm doing a large chunk of the SystemVerilog code (and some C code to control a menu).

It's ongoing for the next two months or so. I can gradually post PCB designs and such we have to come up with.

Basically my lab partner and I are making an FPGA based guitar guitar effects pedal board with routing between external guitar effects pedals and the internal DSP modules we will have.

That is, there are 3 internal DSP modules, you can plug in 3 pedals and route them as you please. Initially we were doing 4 instead of 3, but we decided to cut back to 3 to make things a bit easier (since there are 3 that means there are 3! possible routing combinations, so 6. For 4 there are 24, etc. So this isn't too scalable, but yeah).

If you want I can give you some of the test SystemVerilog I am currently using, though right now it's still pretty early on. Things will be really rolling in the next 2 weeks once we get parts in and start actually testing.

Block diagram:

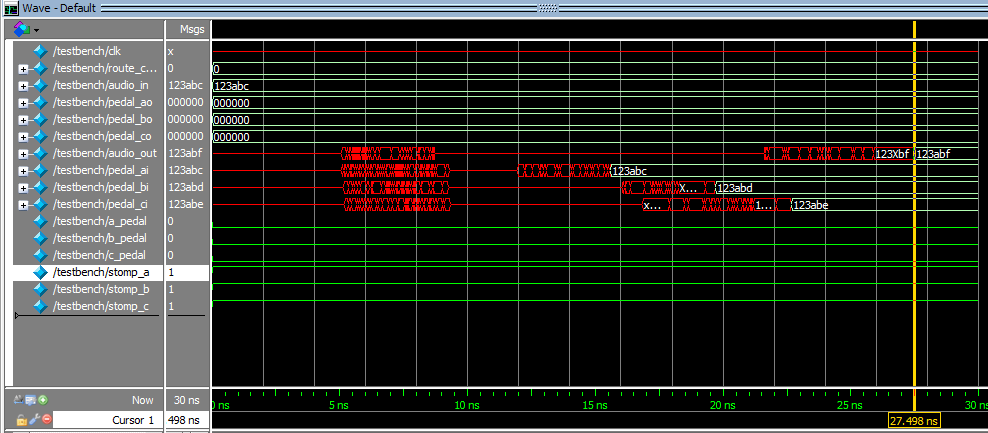

A really quick gate level simulation on the routing:

Demux _24 is a 24 bit 1:4 demux (the non-used outputs are defaulted to 24'b0). mux_24 is a 24 bit 4:1 mux.

This is my senior project, figured I'd share it. I'm doing a large chunk of the SystemVerilog code (and some C code to control a menu).

It's ongoing for the next two months or so. I can gradually post PCB designs and such we have to come up with.

Basically my lab partner and I are making an FPGA based guitar guitar effects pedal board with routing between external guitar effects pedals and the internal DSP modules we will have.

That is, there are 3 internal DSP modules, you can plug in 3 pedals and route them as you please. Initially we were doing 4 instead of 3, but we decided to cut back to 3 to make things a bit easier (since there are 3 that means there are 3! possible routing combinations, so 6. For 4 there are 24, etc. So this isn't too scalable, but yeah).

If you want I can give you some of the test SystemVerilog I am currently using, though right now it's still pretty early on. Things will be really rolling in the next 2 weeks once we get parts in and start actually testing.

Block diagram:

A really quick gate level simulation on the routing:

Code:

module router_control

(

input [2:0] route_case,

output logic [1:0] a_mux, b_mux, c_mux,

output logic [1:0] a_demux, b_demux, c_demux

);

always_comb

begin

a_mux = 2'b00;

b_mux = 2'b00;

c_mux = 2'b00;

a_demux = 2'b00;

b_demux = 2'b00;

c_demux = 2'b00;

case(route_case)

0 : /*default case*/; //abc

1 : begin //acb

a_mux = 2'b00;

b_mux = 2'b10;

c_mux = 2'b10;

a_demux = 2'b01;

b_demux = 2'b10;

c_demux = 2'b01;

end

2 : begin //bac

a_mux = 2'b10;

b_mux = 2'b01;

c_mux = 2'b10;

a_demux = 2'b10;

b_demux = 2'b01;

c_demux = 2'b00;

end

3 : begin //bca

a_mux = 2'b10;

b_mux = 2'b01;

c_mux = 2'b00;

a_demux = 2'b10;

b_demux = 2'b00;

c_demux = 2'b10;

end

4 : begin //cab

a_mux = 2'b01;

b_mux = 2'b00;

c_mux = 2'b01;

a_demux = 2'b00;

b_demux = 2'b10;

c_demux = 2'b10;

end

5 : begin //cba

a_mux = 2'b10;

b_mux = 2'b10;

c_mux = 2'b01;

a_demux = 2'b10;

b_demux = 2'b01;

c_demux = 2'b01;

end

default : ;

endcase

end

endmodule : router_control

Code:

module router(input [1:0] a_mux, b_mux, c_mux,

a_demux, b_demux, c_demux,

input a_pedal, b_pedal, c_pedal, stomp_a, stomp_b, stomp_c,

input [23:0] audio_in, pedal_ao, pedal_bo, pedal_co,

output [23:0] audio_out, pedal_ai, pedal_bi, pedal_ci

);

//internal signals

logic [23:0] a_in, a_out, b_in, b_out, c_in, c_out;

logic [23:0] a_b,a_c,a_o,b_c,b_a,b_o,c_a,c_b,c_o;

//a

mux_24 mux_a(.a(audio_in),.b(b_a),.c(c_a),.d(),.sel(a_mux),.out(a_in));

dsp_pedal a(.audio_in(a_in),.out(a_out),.pedal_out(pedal_ao),.is_pedal(a_pedal),.pedal_in(pedal_ai),.stomp(stomp_a));

demux_24 demux_a(.in(a_out),.sel(a_demux),.out_a(a_b),.out_b(a_c),.out_c(a_o),.out_d());

//b

mux_24 mux_b(.a(a_b),.b(audio_in),.c(c_b),.d(),.sel(b_mux),.out(b_in));

dsp_pedal b(.audio_in(b_in),.out(b_out),.pedal_out(pedal_bo),.is_pedal(b_pedal),.pedal_in(pedal_bi),.stomp(stomp_b));

demux_24 demux_b(.in(b_out),.sel(b_demux),.out_a(b_c),.out_b(b_a),.out_c(b_o),.out_d());

//c

mux_24 mux_c(.a(b_c),.b(audio_in),.c(a_c),.d(),.sel(c_mux),.out(c_in));

dsp_pedal c(.audio_in(c_in),.out(c_out),.pedal_out(pedal_co),.is_pedal(c_pedal),.pedal_in(pedal_ci),.stomp(stomp_c));

demux_24 demux_c(.in(c_out),.sel(c_demux),.out_a(c_o),.out_b(c_b),.out_c(c_a),.out_d());

assign audio_out = (a_o + b_o + c_o);

endmodule : router

Last edited: